1、电路中的开关器件

在电路中,开关是一种我们经常使用的器件。我们希望在某些时刻可以控制电路”有电“和”没电“。日常生活中也有很多类型的开关。但是这些开关大多是机械开关,需要外力来驱动开关闭合或断开。在电路中如果我们想通过信号控制这种开关的断开与闭合恐怕得加一个电机才能做到。那么我们更加希望有一种能够直接通过电信号控制电流流通与否的器件。这种器件就是电子开关器件。

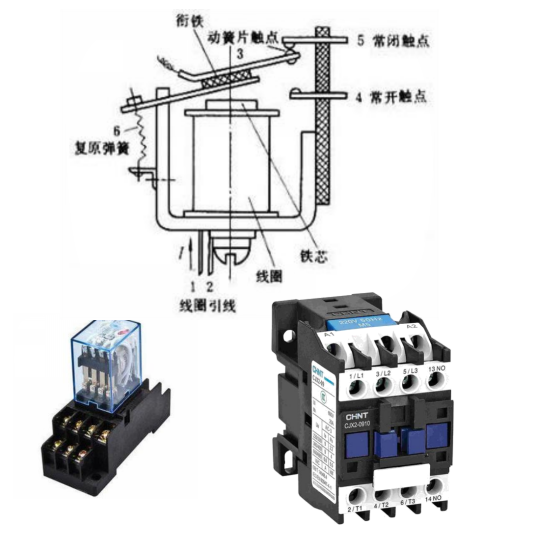

自动电子技术诞生以来,出现了很多种电子开关。最直接能想到的就是我们所说的给机械开关加上一个机构能够通过电信号驱动机械开关的闭合。这种器件就是继电器/接触器。

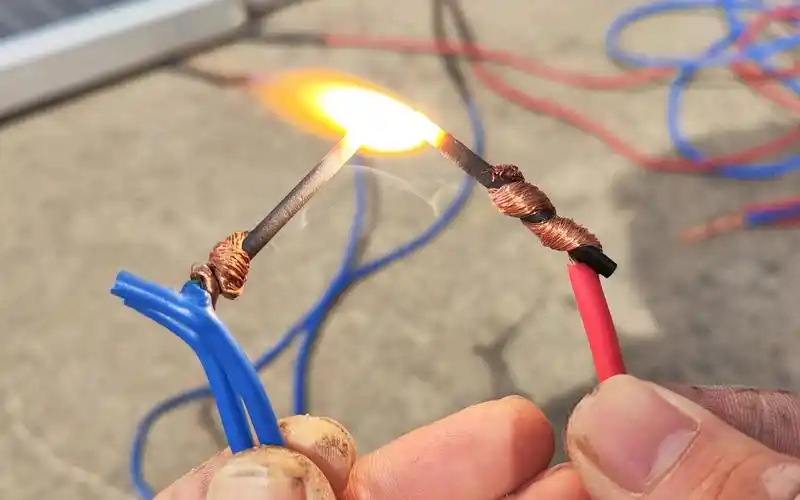

这种器件应用广泛,原理简单。但是也存在问题。就是机械结构的开关其开关的速度有限,最多达到上百Hz。同时由于存在触点,导致断开大电流时容易出现拉弧现象,导致触点烧蚀。

随着半导体技术的发展,晶体管/三极管、MOS管、IGBT等开关器件出现。这种器件没有机械结构,更适用于电子电路实现高速开关。本节具体讲解一下MOS管的应用。

2、MOS管

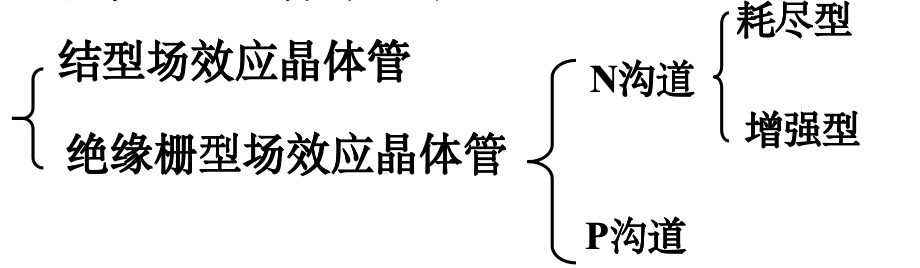

场效应晶体管是用输入回路的电场效应来控制半导体中的多数载流子,使流过半导体内的电流大小随电场强弱而变化,形成电压控制其导电的一种半导体器件。与晶体管相比场效应晶体管更易于集成。MOS管的分类如下所示。

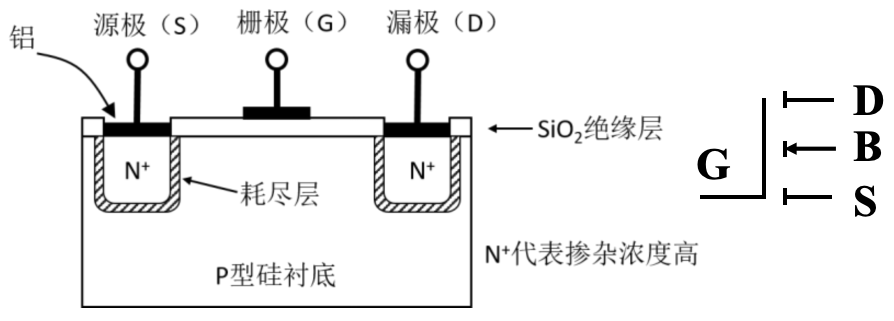

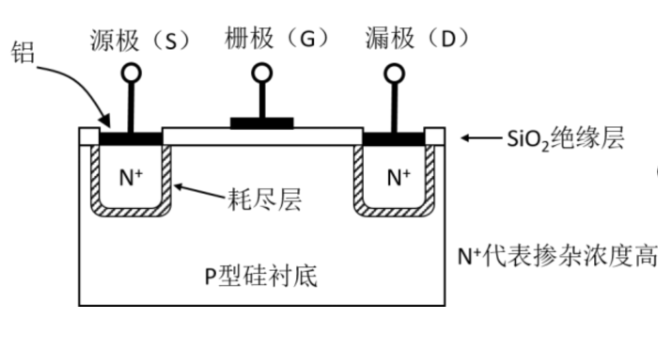

在电子电路中我们更加经常使用增强型的MOS管。如下所示为,增强型N沟道MOS管结构示意图。

在一块掺杂浓度较低的P 型半导体硅衬底上,用半导体光刻、扩散工艺制作两个高掺杂 浓度的N+区,并用金属铝引出两个电极,分别作为漏极 D 和源极 S。然后在漏极和源极 之间的P 型半导体表面覆盖一层很薄的二氧化硅(Si02)绝缘层膜,在在这个绝缘层膜 上装上一个铝电极,作为栅极 G。这就构成了一个 N 沟道增强型 MOS 管。显然它的栅极和其它电极间是绝缘的。

2.1 MOS管开关控制原理

增强型N沟道MOS管在初始状态下源极和漏极之间是无法导电的,原因有二。

① 源极为高掺杂N半导体,衬底是低掺杂P半导体。源极与衬底之间构成了一个源极为阴极、衬底为阳极的二极管(PN结)。而漏极和衬底之间也会构成一个衬底为阳极、漏极为阴极的二极管。且两个二极管方向相反,导致无论是源极到漏极还是漏极到源极均不导电。

② 衬底的掺杂浓度较低,载流子数量较少。

那怎么能让漏极和源极之间导电呢?那就要针对性的消除上面两个因素。

① 想办法让PN结消失

② 增加源极到漏极之间区域的载流子数量

对于增强型N沟道MOS管而言,我们可以在栅极上加一个电场,将大体积的P型衬底里的电子吸引到栅极附近,将栅极附近的空穴排斥到其他区域。这样在栅极附近,半导体的电子数量大大增加,事实上这块区域已经被改性成N型半导体了。这样就会产生两个现象

① 栅极区域的半导体也是N型半导体,和漏极、源极之间的是同一种半导体,PN结消失。

②栅极区域处于源极和漏极之间,载流子(电子)数量增多,导电能力大大增强。

如此一来,我们只需要控制栅极电压即可控制源极和漏极之间的导电特性,也就形成了开关能力。

2.2 MOS管控制电压

2.2.1 N沟道增强型MOS管

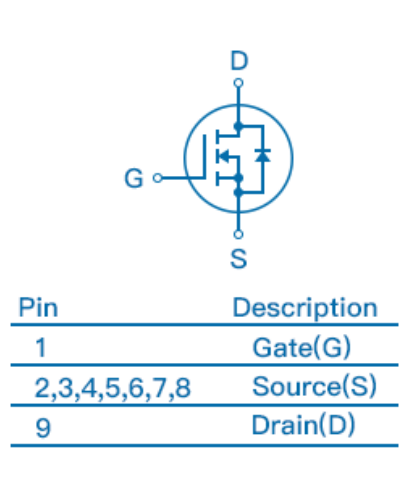

如上图所示,原始的MOS管左右是对称的,难免会有人问怎么区分源极和漏极呢?其实原理上,源极和漏极确实是对称的,是不区分的。但在实际应用中,一般在源极和漏极之间连接一个二极管,起保护作用,正是这个二极管决定了源极和漏极。

现在,我们忽略掉体二极管。由于MOS管具有三个极,而我们想在栅极上加上电场,就势必要从另外两个极中选择一个与栅极构成回路。同时,由于N沟道增强型MOS希望将电子吸引至栅极附近、将空穴排斥出栅极附近,那么栅极就需要作为外加电场的高电势一侧,因此也就是栅极电压要高于另一个参考电压。

对于实际N沟道增强型MOS管而言,由于体二极管的存在,我们肯定希望漏极接高电势,源极接低电势,这样在栅极没有电压时不会有电流从D到S。(考虑一下,如果接反的话,是不是无论G有无高电势都会有电流从S到D?)

而要让MOS管导通时需要让G极具有相对更高的电势,由于N沟道增强型MOS的S极电势较低,而D极电势较高,因此我们为了更好控制一般采取通过让G极电势高于S极即可。也就是让Vgs大于一定的阈值。

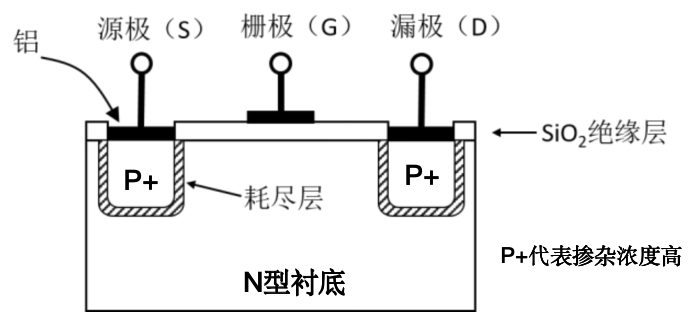

2.2.2 P沟道增强型MOS管

如图所示,P沟道增强型的MOS管,由于衬底是N型,而源、漏两极是P型半导体,因此若希望漏源之间导通,则需要在栅极附近吸引更多的空穴、排斥电子。这需要栅极电场处于相对较低的一侧。也就是从S、D之间选一个和G之间加上一个电场,同时让G处于电势较低的一侧。

同样的,如下图所示,由于实际MOS管中存在体电阻,一般是让P沟道增强型MOS的S极接高电势、D极接低电势。而由于G极的电势相较于另外两个电极之一较低即可,因此一般选电势较高的S极与G极,这样比较容易产生导通条件。

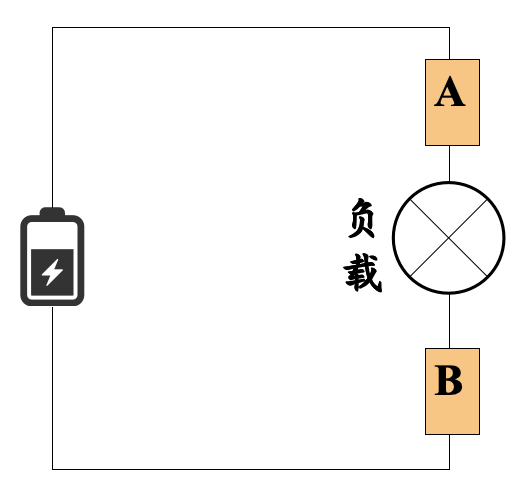

综上,无论是P沟道还是N沟道的MOS管都是通过控制栅源电压来控制MOS管导通与否。那么结合者驱动难以程度(达成栅极较高电势或较低电势的难以程度)P和N沟道增强型MOS更适合分别在下图A、B两个位置呢?

3 高侧驱动和低侧驱动

3.1 P-MOS、N-MOS与高侧、低侧驱动

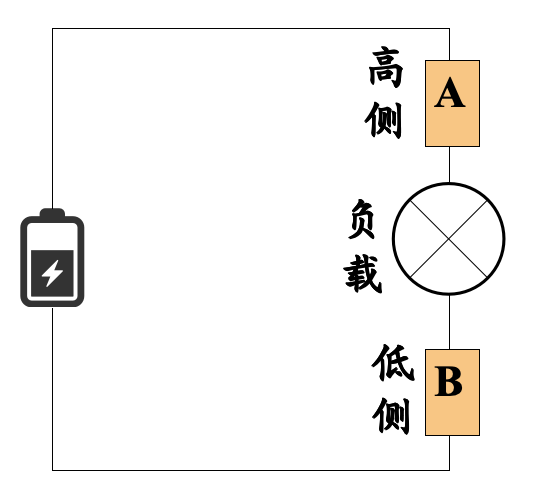

如图所示,A点所在位置由于相对电势较高,因此被称之为高侧/高端;B点所在位置由于相对电势较低,因此被称之为低侧/低端。

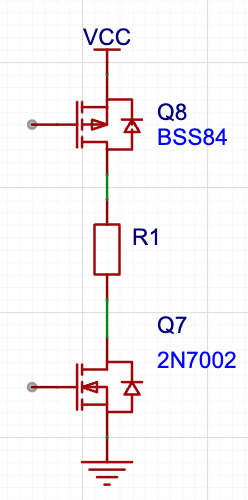

如下图所示,一般P-MOS用于高侧驱动、N-MOS用于低侧驱动。为什么呢?还是要从两种MOS的导通条件来看。首先要明确一个问题,对于通过电阻分压设计的MOS驱动电路来说,栅极电压最大不会超过VCC,最低不会低于GND。

因此,我们以N-MOS来分情况讨论一下:

当N-MOS位于低侧时,S极接GND,D极接负载,那么S极的电势相对D极较低,D极电势相较于VCC较低。那么则很容易通过电阻分压构成一个G极电势高于S极局面。此时MOS管导通。而关断MOS只需要让G极电势与S极相同即可也很容易达成。

当N-MOS位于高侧时,S极接负载,D极接VCC,此时S极电势相对D极还是较低的(由于MOS导通阻抗的存在),但是低多少呢?由于MOS管导通阻抗是毫欧级的,S极和D极的电位差也非常小,甚至可以忽略不计。这就存在问题了,由于G级要比S极电势要高,且要高到一定程度才能形成稳定的沟道。如果希望MOS管导通,那么G极上加载的电势甚至要高于VCC才行。这很明显不是能通过简单电阻分压达到的。

所以,N-MOS一般用于在低侧驱动负载。

相反P-MOS也是类似的情况。

当P-MOS位于高侧的时候,S极接VCC,D极接负载,那么S极的电势相对D极较高。如果需要MOS管导通,只需要通过电阻分压,让G极的电势低于S极即可,也就是低于VCC。需要让MOS管断开,只需要让G极电压等于S极即VCC即可。

当P-MOS位于低侧时,S极接负载,D极接GND,此时S极电势依旧相对D极较高。如果需要MOS管关断只需要让G极接S极也就是负载低侧即可。但是问题在于如果需要MOS管导通,那么就需要G极电势低于S极一定程度,甚至要低于GND。那么很明显也不是通过简单的电阻分压可以形成的。

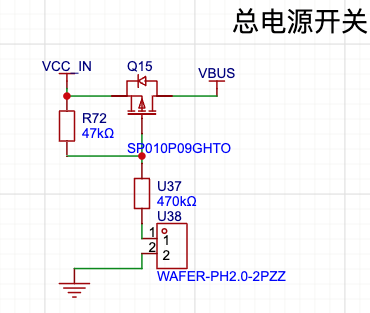

综上所述,N-MOS一般用于低侧驱动;P-MOS一般用于高侧驱动。如下图所示为P-MOS作为电源总开关的电路。

当开关的1、2两个端子不闭合时,栅极电压等于VCC_IN(由于栅极阻抗极高,电流几乎为零)。此时栅源电压为0,无法形成导电沟道。

当开关1、2两个端子闭合时,栅极电压等于47K电阻与470K电阻的分压即10/11 * VCC_IN,栅源电压等于VCC_IN/11。需要注意的是本电路的VCC_IN为48V。其他电路需要根据输入电压确定分压电阻的阻值大小。

3.2 N-MOS用于高侧驱动

N-MOS一般用于低侧驱动;P-MOS一般用于高侧驱动。但是有些时候我们需要高侧驱动(例如用作电子开关,控制一个电路是否有电的时候。)我们会发现市面上大多数大功率的MOS管都是N沟道的MOS管。这是由于生产工艺的问题,导致N沟道的MOS电流容易做的更大。这样导致我们不得不将N沟道MOS用作高侧驱动。

N-MOS用作高侧驱动存在什么问题呢?

问题在于如果N-MOS用作高侧驱动,需要提供一个高于电源电压的控制信号,使得VGS大于阈值。因此在这种场景中,我们的控制信号不能简单的来着单片机或者电阻分压。而是需要专门的驱动电路,也就是基于电荷泵技术的升压电路。

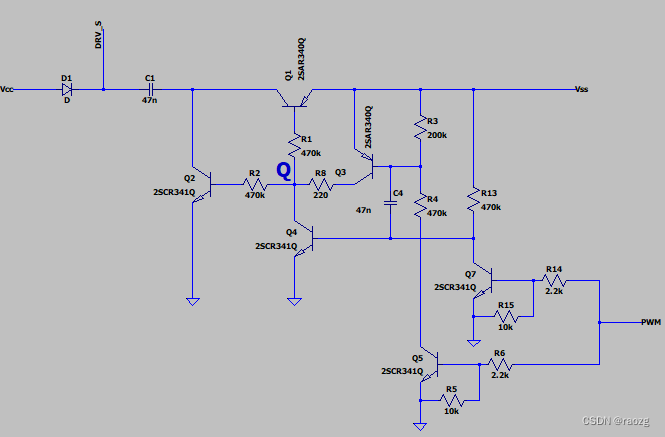

电容自举电路一般由低压电源,隔离二极管,电容,高端电源,2组开关组成。如下图:D1,C1, Q1, Q2组成电容自举电路。当Q2通,Q1关断时,C2被充电到Vcc;随后,Q2关断,Q1通,DRV_S端电压被抬升到 Vcc(15v) + Vss(300v)。DRV_S端即实现了大于Vss的电压值,其中Vcc为NMOS开启电压。Q1、Q2通过Q点电势高低控制通断;Q点电势低时,Q1导通,Q2关闭;Q点电势高时,Q1关闭,Q2导通;此方式可避免Q1、Q2同时导通导致的短路电流。

单高端NMOS驱动: C4为Q3关断加速电容,频率提升时,Q3关断延时将会导致Q3/Q4短暂短路。

也有集成电路可选,例如: